# **COMPUTER GRAPHICS**

**APPLICATION MANUAL**

1<sup>st</sup> EDITION

**JUNE 1993**

#### Copyright INMOS Limited 1993

The color images shown in this manual are taken from the IMS G173/4 demonstration, Copyright INMOS Limited 1992, 1993. All rights reserved (except "Mount Mandelbrot", which was rendered using the Povray imaging package).

IMS and PixMix are trademarks of INMOS Limited.

IBM, PS/2, and Micro Channel are registered trademarks of IBM.

XGA is a trademark of IBM licensed to SGS-THOMSON.

TARGA is a trademark of TrueVision.

INMOS Limited is a member of the SGS-THOMSON Microelectronics Group.

SGS-THOMSON reserves the right to make changes in specifications at any time and without notice. The information furnished by SGS-THOMSON in this publication is believed to be accurate; however, no responsibility is assumed for its use, nor for any infringement of patents or other rights of third parties resulting from its use. No licence is granted under any patents, trademarks or other rights of SGS-THOMSON.

Document number: 72 TRN 250 00

Order Code: AMCOMGRAST/1

## **TABLE OF CONTENTS**

| INTRODUCTION                  | Page | V   |

|-------------------------------|------|-----|

| GENERAL INDEX                 |      | ix  |

| COLOR IMAGE EXAMPLES          |      | 1   |

| PALETTE-DAC APPLICATION NOTES |      | 11  |

| CVC APPLICATION NOTES         |      | 41  |

| GRAPHICS GLOSSARY             |      | 149 |

| ORDERING INFORMATION          |      | 157 |

The Computer Graphics Applications Notebook contains Application Notes intended for system designers using the SGS-THOMSON range of computer graphics devices. A brief summary of the Application Notes included in this book is given later in this introduction.

This Applications Notebook should be used in conjunction with the *Computer Graphics Databook*, 3rd edition, SGS-THOMSON, November 1992 (Order code DBGRAPHICST/2).

#### THE COMPANY

SGS-THOMSON is an international semiconductor company founded in 1987 as a result of the merger of Thomson Semiconducteurs and SGS Microelettronica. In April 1989, SGS-THOMSON further enhanced its international position with the acquisition of INMOS, a British company with leading MOS technology. The part of INMOS responsible for the computer graphics products described in this book is now the Graphics Business Unit of SGS-THOMSON.

SGS-THOMSON has earned a leading position in the world semiconductor market with its rich technological background, considerable production resources, and broad product range which covers all sectors of advanced electronics. According to Dataquest, the most respected market analysts in the semiconductor field, in 1992 SGS-THOMSON, with a sales growth of 12%, outgrew the market growth by two points and with sales over 1.6B US\$ confirmed its position of 13th in the worldwide rankings and second European in the worldwide arena.

The combined forces of the Group total 15 production locations, 9 advanced research and development centers, 25 design centers, 44 direct sales offices in 21 countries, and over 600 representatives and distributors.

To guarantee continued technological development and consistently leading edge products, SGS-THOMSON each year invests close to 20% of its sales figures in R&D and is a key player in Europe's advanced technology research programs.

#### THE PRODUCTS

SGS-THOMSON's computer graphics devices provide, at a basic level, the data conversion and analog output stage to drive a color monitor. The more advanced products integrate further stages and functions of the graphics subsystem. The products cover a wide spectrum of performance and applications in PCs and workstations.

#### **PALETTE-DACS**

Palette-DACs are primarily used in PCs which provide VGA standard graphics capability, and in VGA add-in boards. The IMS G171, which rapidly became the industry standard for VGA graphics systems, was adopted by IBM for use in the IBM PS/2 range of PCs. SGS-THOMSON has now shipped well in excess of 30 million Palette-DACs.

The recently introduced IMS G173 and G174 support the high color and true color modes now offered by many VGA controllers. They allow mixed format display onscreen, making them ideal for windowing applications, and increase the number of simultaneously displayable colors from the 256 of standard VGA to 32K (16-bit) or 16 million (24-bit).

SGS-THOMSON also offers a "semi-custom" facility for graphics products using a library of dedicated graphics cells, including PLL, DAC and RAM macro-cells. The customer interface for this can range from complete customer design to SGS-THOMSON supplied turnkey solutions. This technique is used also for new standard products, including the STG 1700, a 16-bit pixel interface Palette-DAC featuring 135MHz video speed (supporting  $1280 \times 1024$  resolution at 76Hz screen refresh) using an on-chip clock doubler (therefore a simple  $67.5 \mathrm{MHz}$  pixel interface).

#### **COLOR VIDEO CONTROLLERS**

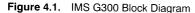

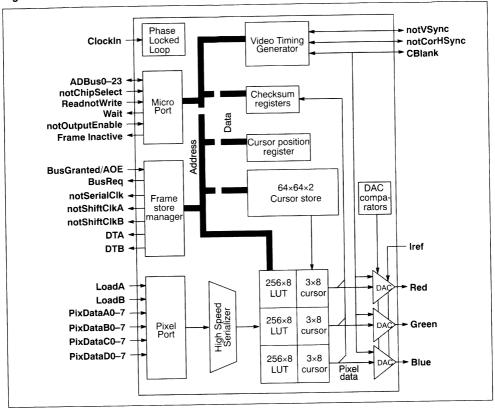

The Color Video Controller (CVC) takes functional integration a significant step further, and represents a complete graphics subsystem on a chip. The devices integrate a triple DAC and look up table with a programmable video timing generator, framestore manager, phase locked loop for clock generation, pixel multiplexer and hardware cursor. Applications are mainly in high resolution PC add-in boards and processor direct graphics PCs.

#### **FUTURE GRAPHICS PRODUCTS**

SGS-THOMSON is constantly upgrading and developing its product ranges. The Company will continue to develop highly integrated and cost effective products for use in color graphics systems in response to customer requirements and evolving markets, targeting especially the volume PC markets, and striking a balance between new product innovation and established industry standards.

#### **SUMMARY OF APPLICATION NOTES**

#### PALETTE-DACS

#### 1. IMS G173/4 compatibility and hardware design

This note highlights a number of issues relating to the use of the IMS G174. BIOS support, Palette-DAC identification, competitors' part functionality and compatibility and layout issues are discussed.

#### 2. Designing with the IMS G177

This note shows how VGA chipsets control the power-down states of the IMS G177. A brief competitive analysis of alternative devices is also given.

#### **COLOR VIDEO CONTROLLERS**

#### 3. 32-bit Color Video Controller upgrade compatibility: a design guide

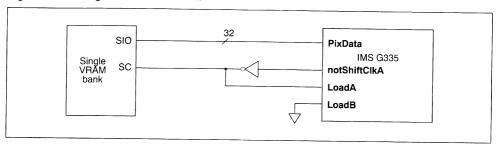

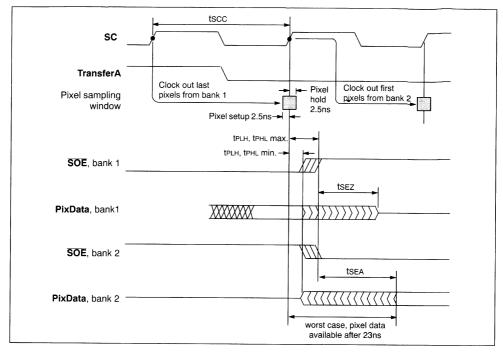

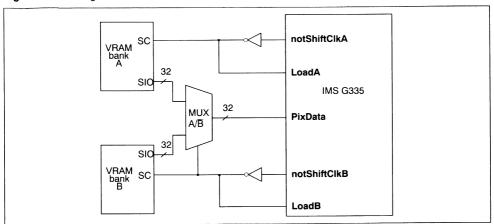

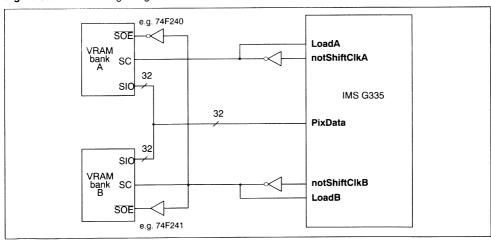

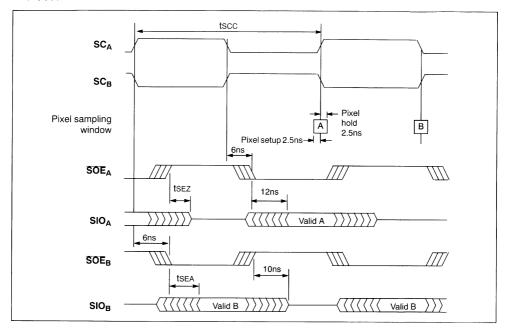

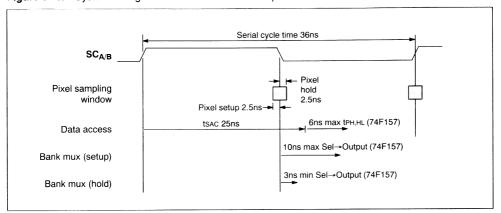

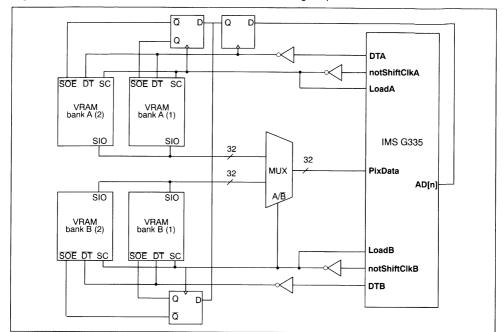

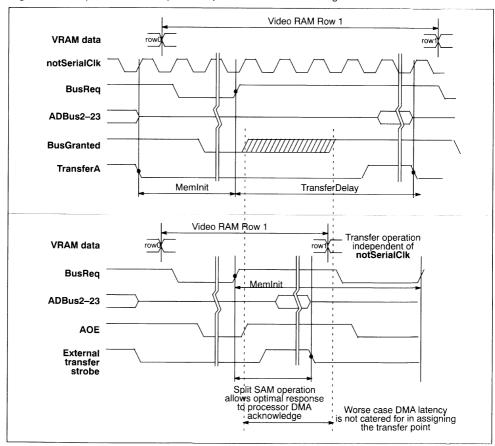

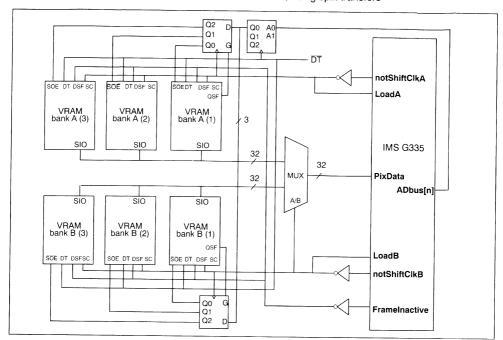

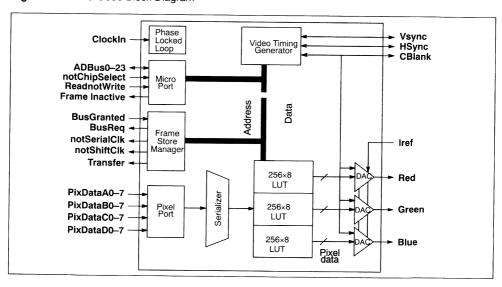

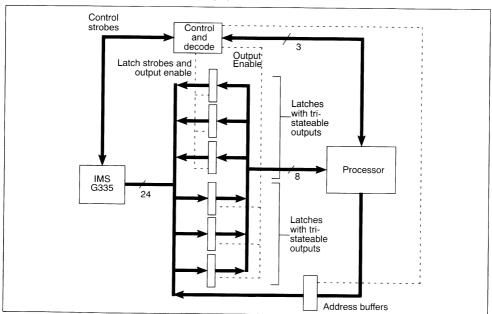

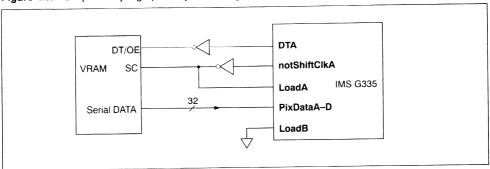

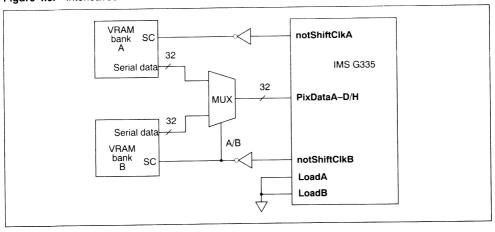

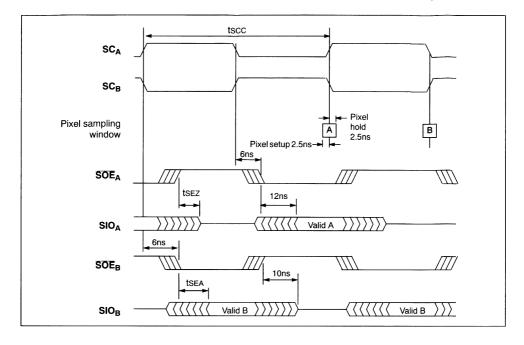

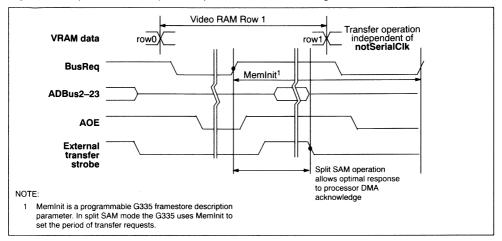

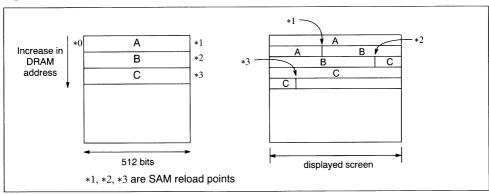

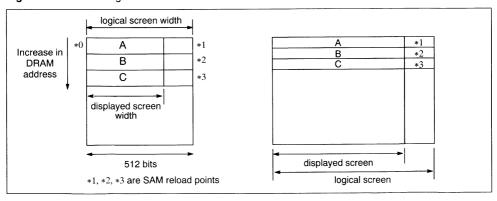

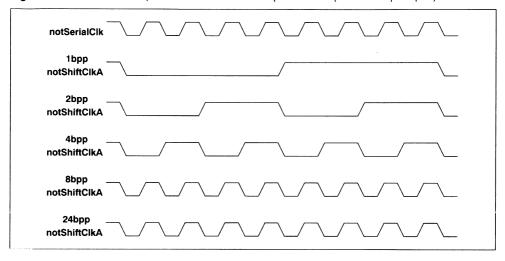

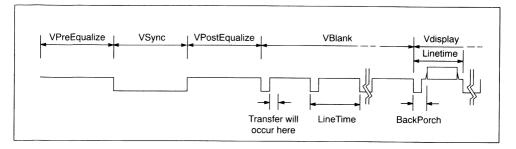

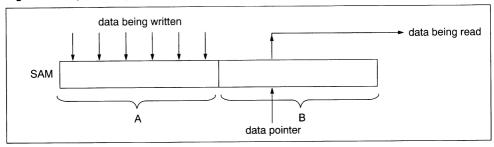

This Application Note overviews the implementation of the IMS G332 Color Video Controller in graphics designs requiring upgradability to the new IMS G335 controller. New features discussed include split SAM support, asynchronous micro port and the new pixel sampling mechanism allowing  $1280 \times 1024 \ 15/16$ -bit pixels to be displayed at a 76Hz refresh rate. General design implementations include single and multiple VRAM banks, bank interleaving for improving VRAM SAM access latency with and without pixel multiplexors (using Serial Output Enable).

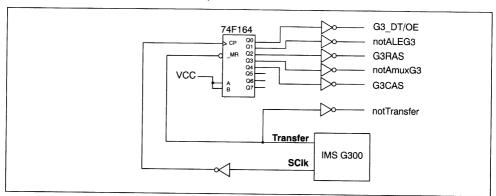

#### 4. Migrating G300x designs to a G335 solution

This note identifies the changes required in converting designs currently using the now obsolete IMS G300 to systems with similar functionality but offering improved or more features using an IMS G335. Micro port, split SAM transfer and software issues are discussed.

#### 5. Hardware design with CVCs

This note discusses and provides recommendations on the analog design, circuit layout and routing of CVC based graphics printed circuit boards (PCBs). These recommendations aim to minimize interactions between digital and analog signals in the same area of a PCB, which in turn provide clean DAC outputs and a screen display free from effects relating to Shift Clock frequencies, DRAM refresh or other digital "events".

#### 6. Compact design considerations when using the IMS G335

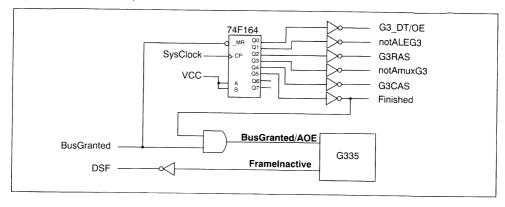

This note overviews the design of a microprocessor-based graphics module using the IMS G335 as the local display controller. The design effectively implements a processor direct graphics solution in an area approximately equal to a standard credit card. The note discusses the use of high density/small package EPLDs and other methods of minimizing interface logic. Concentrating on this requirement, the IMS G335's pixel multiplexor is implemented using Serial Output Enables.

This provides a suitable system for sampling 16-bit pixels and displaying frequencies up to 95MHz with the chosen VRAM devices.

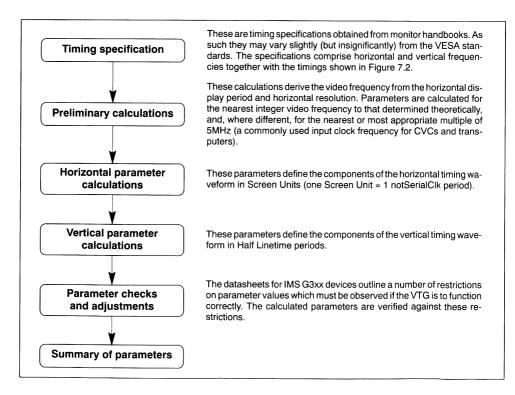

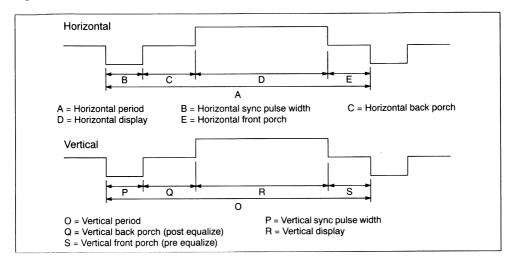

#### 7. CVC parameter calculations for driving standard PC displays

This note derives the CVC parameters required for driving standard PC resolutions. Attention is paid to meeting the CVC timing specifications.

#### 8. Driving PAL and NTSC with CVCs

CVCs can drive arbitrary resolutions including both PAL and NTSC. This note derives the parameters required to drive these two standards. Particular attention is paid to meeting the PC display timing specifications.

#### 9. Using the CVC automatic screen refresh

This note explains the programming of the IMS G335 CVC when implementing its automatic screen refresh feature. A variety of screen modes are discussed to clarify some of the issues involved.

#### 10. Using CVCs in slave mode

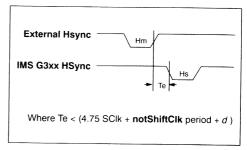

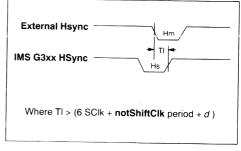

The requirements of the CVC slave mode are explained, including external (master) HSync and VSync timings, pixel level synchronization, brief genlocking requirements, slave delay, sync pulse level considerations and control register bit settings. Interlaced and non-interlaced operation are covered.

#### 11. Using the on-chip self test capabilities of CVCs

One of the areas of most concern within the computer industry is the area of testability. The ability to accurately test machines accrues benefits to both manufacturer and end user.

To satisfy this need, this Application Note describes how using the on-chip self test capabilities of a CVC, the correct operation of the serial access data path from VRAM right up to the data presented to the triple video DACs within the CVC may be verified. This verification is performed at video data rates.

#### 12. Some common problems driving monitors with CVCs

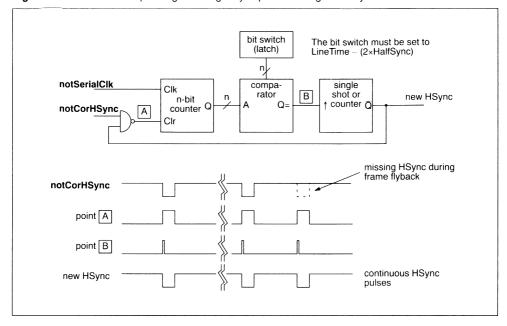

The connection of multiple sync signals and the lack of HSync pulses during frame flyback (on the IMS G332 and G364 only) can cause problems with certain monitors. This note discusses some solutions.

#### **GENERAL INDEX**

|                                                                             | Page |

|-----------------------------------------------------------------------------|------|

| PALETTE-DAC APPLICATION NOTES                                               |      |

| AN605 - IMS G173/4 Compatibility and Hardware Design                        | 13   |

| AN606 - Designing with the IMS G177                                         | 37   |

| CVC APPLICATION NOTES                                                       |      |

| AN607 - 32-bit Color Video Controller Upgrade Compatibility: a Design Guide | 43   |

| AN608 - Migrating G300x Designs to a G335 Solution                          | 69   |

| AN609 - Hardware Design with CVC                                            | 79   |

| AN610 - Compact Design Considerations When Using the IMS G335               | 87   |

| AN611 - CVC Parameter Calculations for Driving Standard PC Displays         | 95   |

| AN612 - Driving PAL and NTSC with CVCs                                      | 115  |

| AN613 - Using the CVC Automatic Screen Refresh                              | 125  |

| AN614 - Using CVCs in Slave Mode                                            | 133  |

| AN615 - Using the on-chip Self Test Capabilities of CVCs                    | 139  |

| ANG16 - Same Common Problems Driving Manitors with CVCs                     | 115  |

## **COLOR IMAGE EXAMPLES**

#### **COLOR IMAGE EXAMPLES**

The color image examples in this section emphasize the features of the SGS-THOMSON IMS G173/4 range of Palette-DACs. Three different resolutions and pixel depths are used: 8 bits per pixel (bpp) at  $1024 \times 768$ , 16bpp at  $800 \times 600$ , and 24bpp at  $640 \times 480$ . A number of factors important to achieving the best possible color graphics display are highlighted, including:

- The effect of different pixel depths when shading

- Using High Color to overcome the limitations of indirect color when using multiple windows

- The effect of different pixel depths and display resolution when rendering

- · Mixing different pixel formats using PixMix

- The need for 24 bits per pixel

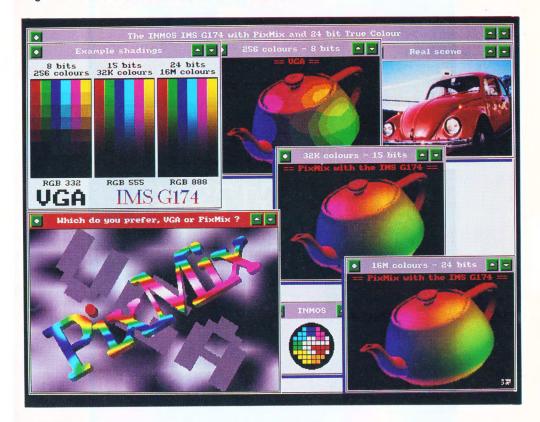

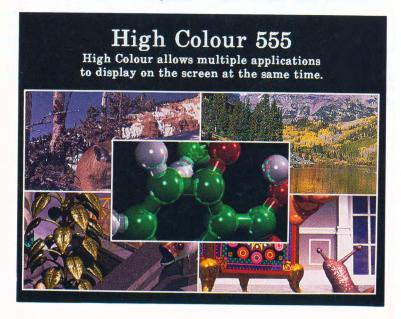

Figure 1. The IMS G173/4 launch and brochure image

Figure 1 is the 24 bits per pixel image used for the IMS G173/4 brochure and launch. It shows example shadings, a 3D CAD object at 8, 15 and 24 bits per pixel, compares the color "PixMix" with the monochrome "VGA", and includes a real scene at 24 bits per pixel.

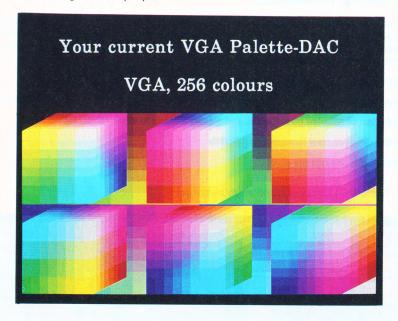

Figure 2. Shaded image at 8 bits per pixel

Figure 3. Shaded image at 16 bits per pixel

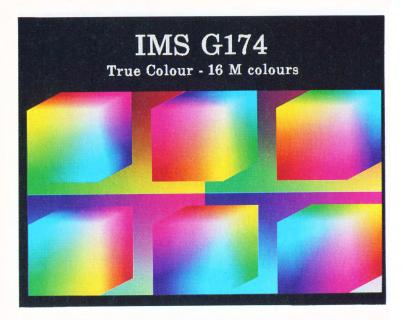

Figure 4. Shaded image at 24 bits per pixel

## The effect of different pixel depths when shading

Figures 2, 3 and 4 clearly show the differences between 8, 16 and 24 bits per pixel when shading. Note that in Figure 2 using 8 bits per pixel, the shading is quite coarse. Figure 3 shows the improvement achieved using 16 bits per pixel, but 24 bits per pixel, as shown in Figure 4, is really needed for correct shading, .

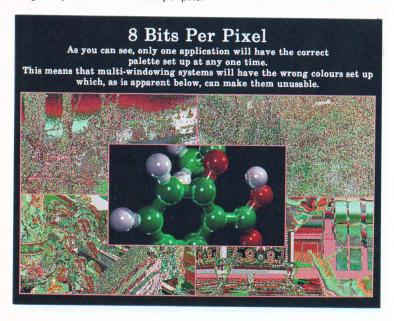

#### Examples of using multiple windows

Using 8 bits per pixel can lead to palette problems when using multiple windows. In Figure 5 using 8 bits per pixel, only one window can have its correct palette loaded at any one time. As can be seen, this can make the other windows unusable. Figure 6 shows the advantages of High Color, as all the windows can use their correct colors.

Figure 5. Using multiple windows at 8 bits per pixel

Figure 6. Using multiple windows with High Color

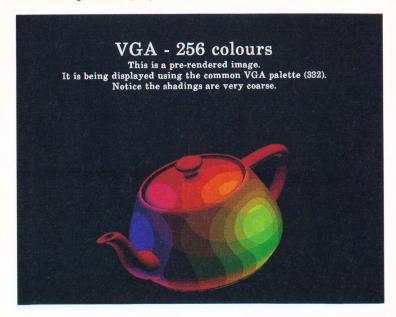

Figure 7. Rendered image at 8 bits per pixel

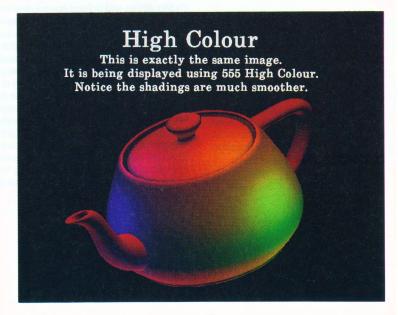

Figure 8. Rendered image at 16 bits per pixel

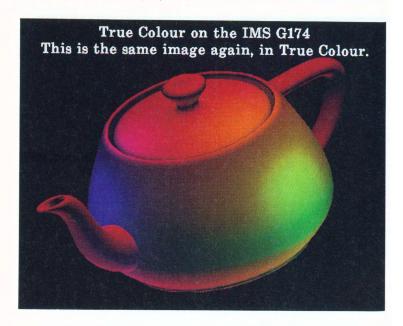

Figure 9. Rendered image at 24 bits per pixel

## The effect of different pixel depths when rendering

These images show the differences between different pixel depths when rendering the same object (in 3D CAD, for example). Figure 7 shows that the color shading possible with 8 bits per pixel is very limited, resulting in very coarse color graduations. Figure 8 illustrates that while the color shading is dramatically improved by using 16 bits per pixel, 24 bits per pixel are really needed for professional color shading. Note that because different pixel depths are used, different resolutions must be used and consequently the same image is displayed at a different size.

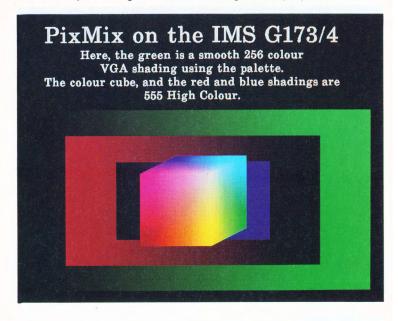

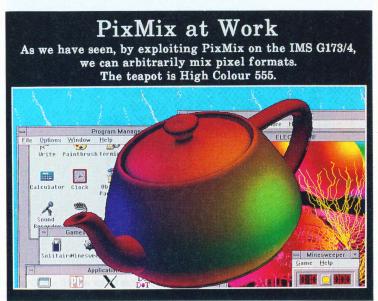

#### PixMix in operation on the IMS G173/4

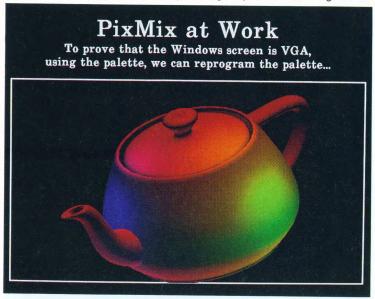

PixMix allows soft or hard control over the dynamic mixing of pixel formats. No other Palette-DAC in the world can do this. Figure 10 shows a subtle green shading using the VGA palette at 8 bits per pixel. The red and blue shadings, and the color cube are 5:5:5 High Color. There are advantages of retaining VGA compatibility. The green shading is a 256 color shading - better and smoother than that obtainable using 5:5:5 High Color, which would limit the shading to 5 bits per color field (32 levels of color). Also because the VGA pixels are using the palette, you can change the palette contents (as with Figure 12). This also retains the ability to perform simple animation and special effects using the palette. which cannot be performed using 16-bit High Color or 24-bit True Color.

Figure 10. PixMix example showing effect of VGA shading at 8 bits per pixel

Figure 11. Example of using PixMix to display different pixel formats

Figure 12. Example showing the effect of reprogramming the palette when using PixMix

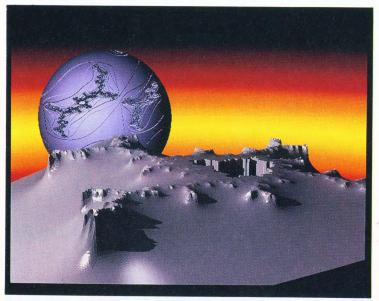

Figure 13. Mount Mandelbrot

Figure 13 is an example of the need for 24bpp, showing 24-bit True Color at  $640 \times 480$  on the IMS G174. The subtle and realistic shadings of the sky, planet and mountain require the color depth of 24bpp, otherwise color quantization bars would be visible and would detract from the aesthetic quality of such an image.

## PALETTE-DAC APPLICATION NOTES

#### **APPLICATION NOTE**

## IMS G173/4 COMPATIBILITY AND DESIGN CONSIDERATIONS

#### GRAPHICS APPLICATIONS GROUP, BRISTOL

| 1.1 | INTRO | DUCTION                                                    | 14 |

|-----|-------|------------------------------------------------------------|----|

| 1.1 | PALET | re-dac compatibility                                       | 15 |

| 1.2 |       | DAC IDENTIFICATION                                         | 15 |

|     | 1.2.1 | USING THE IMS G174/3 AS A REPLACEMENT PART FOR OTHER       |    |

|     | 1.2.2 | PALETTE-DACS                                               | 18 |

|     | 1.2.3 | DIVEL MODES                                                | 19 |

|     | 1.2.4 | PINOLIT DIFFERENCES, MEANINGS AND EXTRA PINS               | 19 |

|     | 1.2.5 | PIXMIX                                                     | 20 |

|     | 1.2.6 | DAC GAIN AND DAC FADE                                      | 20 |

|     | 1.2.7 | XGA REGISTERS                                              | 20 |

|     | 1.2.8 | YGA CURSOR                                                 | 20 |

| 1.3 | USING | THE ON-CHIP SELF TEST FACILITIES OF THE IMS G173/4         | 21 |

|     | 1.3.1 | BENEFITS TO THE MANUFACTURER AND END USER                  | 21 |

|     | 1.3.2 | IMS G173/4 CHECKSUM REGISTERS                              | 21 |

|     | 1.3.3 | CALCULATING THEORETICAL CHECKSUM VALUES                    | 22 |

|     | 1.3.4 | READING THE HARDWARE CHECKSUMS FROM THE IMS G174           | 23 |

|     | 1.3.5 | READING THE CHECKSUM REGISTERS                             | 23 |

|     | 1.3.6 | VGA MODE                                                   | 24 |

| 1.4 | ANALO | OG CONSIDERATIONS                                          | 25 |

|     | 1.4.1 | SUMMARY                                                    | 25 |

|     | 1.4.2 | COMPONENT PLACEMENT                                        | 25 |

|     | 1.4.3 | POWER SUPPLY REQUIREMENTS                                  | 25 |

|     | 1.4.4 | DAC OUTPUTS                                                | 25 |

|     | 1.4.5 | DIGITAL INPUTS                                             | 25 |

|     | 1.4.6 | RFI                                                        | 26 |

|     | 1.4.7 | REFERENCE CIRCUITRY                                        | 26 |

| Α   | APPE  | NDIX                                                       | 27 |

|     | A.1   | EXAMPLE ROUTINE TO SET PIXEL COMMAND AND MASK REGISTERS TO | 27 |

|     |       | POWER-UP VALUES                                            | 27 |

|     | A.2   | EXAMPLE PROGRAMS FOR READING AND CALCULATING CHECKSUMS     | 30 |

|     | A.3   | SETTING THE G174 INTO XGA MODE                             |    |

|     | A.3.1 |                                                            |    |

|     | A.3.2 | WAITING FOR FRAME FLYBACK                                  |    |

|     | A.3.3 |                                                            | -  |

|     | A.3.4 |                                                            |    |

|     | A.3.5 |                                                            |    |

|     | A.3.6 |                                                            |    |

|     | A 3 7 | HEADING UNEUROUND                                          |    |

#### 1.1 INTRODUCTION

This Application Note covers design and compatibility aspects of the SGS-THOMSON IMS G173 and G174 Palette-DACs. The areas covered include functional compatibility with VGA controllers.

hardware and software compatibility with Palette-DACs offered by other manufacturers, comparison of IMS G173 and G174 functionality, and design issues including on-chip self test and use of Iref and Vref modes

**Table 1.1.**

| Part No  | Pixel Rates (MHz) | DAC Resolution | Colors | Features                                                                                   | Package                                    |

|----------|-------------------|----------------|--------|--------------------------------------------------------------------------------------------|--------------------------------------------|

| IMS G176 | 40, 50, 66, 80    | 6-bits         | 256    | Anti-Sparkle,<br>supports SVGA                                                             | 28 pin DIP,<br>32 pin PLCC,<br>44 pin PLCC |

| IMS G173 | 80                | 6-bits         | 64K    | IMS G176 features plus software<br>PixMix, DAC-gain/fade, 16-bit<br>formats                | 44 pin PLCC                                |

| IMS G174 | 80,85,100         | 6/8-bit        | 16M    | IMS G173 features plus hard-<br>ware PixMix, DAC gain and<br>auto-fade, 24-bit format, XGA | 44 pin PLCC                                |

#### Palette-DAC functionality and features

#### VGA compatibility

The entire Palette-DAC family from SGS-THOMSON is VGA compatible. In addition, upgrading from the IMS G176 to G173 or G174 ensures backward compatibility in all cases.

#### DAC resolution

The IMS G174 has an 8-bit DAC resolution. This gives a total color choice of 16 million colors, using 24 bits per pixel. This brings photo-realistic images to the PC screen. All other devices have 6-bit DAC resolution, offering a total choice of 256K colors.

#### High color and true color support

The IMS G173 and G174 both support 16-bit 5:5:5 (RGB) TARGA, 5:6:5 XGA, 6:6:4 i860 and Select:5:5:5 formats, giving more choice for high color displays. The IMS G174 also supports 8:8:8 in 24-bit true color mode.

#### PixMix

The PixMix feature, allowing intermixing of high color and pseudo color on a pixel by pixel basis, is described in Section 1.2.5

#### DAC-fade

The IMS G173/4 DAC fade feature is described in Section 1.2.6.

#### 1.2 PALETTE-DAC COMPATIBILITY

#### 121 DAC IDENTIFICATION

## Access to extended register space (magic access)

To extend the register space whilst maintaining compatibility with existing Palette-DACs, all high color Palette-DACs use a special access technique (magic access). Reading the Mask Register (address 03C6h) four times in succession causes the next access to be directed to a Pixel Command Register. This Pixel Command Register controls the interpretation of pixel data presented at the pixel port, thus allowing 16 and 24-bit pixels to be constructed. Reading or writing any other valid address resets the special access sequence.

Different makes of high color Palette-DAC differ slightly in their implementation of this special access technique, and it is this aspect, along with other minor differences, which allow high color Palette-DACs to be identified.

In Appendix A an example assembler routine is presented which identifies the following five common makes of high color Palette-DAC:

```

SGS-THOMSON IMS G174

AT&T 20C491

Sierra SC11483 / SC11486

Acumos ADAC1

Music MU9C4870V

```

#### **Purpose of Palette-DAC Identification**

Most Palette-DACs are compatible at the Pixel Command Register level for 16bpp operation, but there is no standard for 24bpp operation. Each Palette-DAC therefore must potentially be programmed with different values. Identification of the Palette-DAC being used is straightforward and allows a generic BIOS to be used across several products using different Palette-DACs.

#### Identification of a High Color Palette-DAC

Reading the Mask Register 4 times in succession should cause the next access to be directed to a Pixel Command Register. So the sequence:

```

mov dx, 03c6h

in al, dx ; 1st mask read

in al, dx ; 2nd mask read

in al, dx ; 3rd mask read

in al, dx ; 4th mask read

in al, dx ; read pixel command register

```

should read the Pixel Command Register. This register is initialized to 00h on power-up but if the contents of this register cannot be assumed, the sequence:

```

; clean start, mask := ff, cmd reg := 0

mov dx, 03c9h

; reset seq

in al, dx

mov dx, 03c6h

in al, dx

in al, dx

in al, dx

in al, dx

mov al, 0

; cmd reg := 0

out dx, al

mov dx, 03c9h

; reset seq

in al, dx

mov dx, 03c6h

mov al, Offh

; mask := ff

out dx, al

```

#### IMS G173/4 COMPATIBILITY AND DESIGN CONSIDERATIONS

will write 0 to the Pixel Command Register (if it exists) and 0FFh to the Mask Register, thus setting the command register and mask to known values. Note the order of this, so that if the part is not a high color Palette-DAC, the mask will still be initialized to 0FFh. Reading the Pixel Command Register after such a sequence should access 0 if the device is a high color Palette-DAC. If 0FFh is read, then the device is a normal Palette-DAC.

The implementation of the special (magic) access sequence necessary to access the Pixel Command Register varies slightly from one make of Palette-DAC to another.

The SGS-THOMSON IMS G173/4 reads the Mask Register four times in order to access the Pixel Command Register, as normal. Following this convention, reading the Pixel Command Register four times in succession allows the next access to be made to the XGA Enable Register. The next access will access the Mask Register again, resetting the magic access sequence. As with normal special (magic) access sequences, accessing any other valid address will reset this sequence.

Sierra Palette-DACs (SC1148X) after four successive reads of the Mask Register allow access to the Pixel Command Register until it is written or another valid address is accessed.

AT&T and ACUMOS Palette-DACs (AT&T 20C491, ACUMOS ADAC1) allow just one access to the Pixel Command Register, before reverting to the Mask Register again.

Music Palette-DACs (MU9C4870V) read the Mask Register three times, then read a device ID byte (088h or 089h), then allow access to the Pixel Command Register. Subsequent reads continue to access the Pixel Command Register until it is written or another valid address is accessed.

Reads of the Mask Register can therefore be summarized (assuming that 0FFh is in the Mask Register, and 0 is in the Command Register, and that the special access sequence has been reset):

| Read value sequence                      | Device type                   |  |

|------------------------------------------|-------------------------------|--|

| 0FFh 0FFh 0FFh (not 0FFh) 0 0 0 0 0 0    | Music MU9C4870V               |  |

| OFFh OFFh OFFh O OFFh<br>OFFh            | ATT 20C491, Acu-<br>mos ADAC1 |  |

| OFFh OFFh OFFh OFFh O O O O O OFFh OFFh  | SGS-THOMSON<br>IMS G173/4     |  |

| 0FFh 0FFh 0FFh 0 FFh 0 0 0 0 0 0 0 0 0 0 | Sierra SC1148X                |  |

In the example routine shown in Appendix A, these special access sequences are used to identify the Palette-DAC to be one of the five makes listed above. In addition, the AT&T Pixel Command Register bit 1 controls the palette operation mode (whether 6 or 8 bit), and assuming that the **8not6** pin is connected to logic 0, then this feature may be used to identify the AT&T device. Having written 0FFh to the palette, reading in 6-bit mode will read 03Fh, whereas reading in 8-bit mode will read 0FFh.

If 0FFh is written to the ACUMOS Pixel Command Register, then 0Bh is read back.

#### Summary

Using these characteristics, it is possible to identify which Palette-DAC is being used. This allows a generic BIOS to be used across several products and different Palette-DACs, thus ensuring correct Palette-DAC operation.

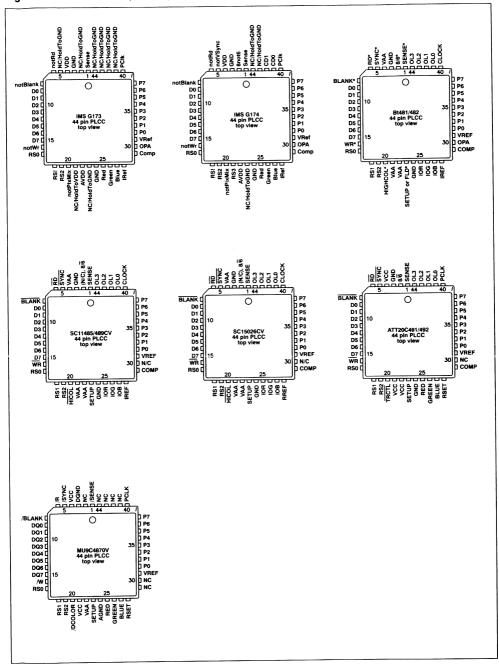

Figure 1.1. Palette-DAC pinouts (44 pin PLCC J-bend package)

#### 1.2.2 USING THE IMS G174/3 AS A REPLACEMENT PART FOR OTHER PALETTE-DACS

#### Replacing the IMS G176 with the IMS G174/3

The IMS G173 and IMS G174 are backwards compatible with the IMS G176. **Iref** (pin 28 on PLCC) and **Comp** (Pin 29) should be connected as shown in Figure 1.4 of Section 1.4 (Analog considerations). This is normally the case in most VGA designs.

#### Replacing the SC11485/6/7 with the IMS G173

The IMS G173 can be used as a replacement for the SC11485/6/7. All high color modes on the SC11485/6/7 are implemented on the IMS G173.

Overlays and Sync pedestal are not available on the IMS G173.

The Pixel Command Register values are the same for all devices as shown in Table 1.2. Software Palette-DAC identification should identify the IMS G173 as being compatible with the SC11485/6/7.

#### Replacing the SC11489 with the IMS G174

The SC11489 is backwards compatible with the SC11485/6/7, with the addition of 8-bit DACs. The IMS G174 can be used as a replacement for the SC11489 but does not supply Sync pedestal and overlays. The Pixel Command Register values are identical for both devices as shown in Table 1.2.

The pinout of the SC11489 and the IMS G174 are shown in Figure 1.1.

### Replacing the SC15025/SC15026 with the IMS G174

The SC15025/SC15026 devices are very similar to the SC1148X devices, with the addition that they support multiple 32K color palette, selectable by register, and a 24-bit true color facility, which can be gamma corrected. The SC15025/SC15026 has the ability to latch 32-bit data as RGBX, on rising edges of latching clock only and rising and falling edges of latching pixel clock.

The SC15025 is similar to the SC15026 but does not support overlays or sync information on the DAC outputs.

The IMS G174 could be used as a replacement for the SC15025/SC15026 but will not be compatible for the 32-bit RGBX mode, overlays and Sync pedestal.

#### Replacing the ATT20C492 with the IMS G173

The ATT20C492 is a 6-bit DAC device that supports 6:6:6, 5:6:5 and 5:5:5 high color modes as well as 8-bit pseudo color (256 color). The ATT20C492 has no sync enable on the RGB DAC outputs.

The IMS G173 and ATT20C492 pinouts are shown in Figure 1.1.

The user should be made aware of the differences in values programmed into the Pixel Command registers of the IMS G173 and the ATT20C492 for certain pixel modes shown in Table 1.2.

The IMS G173 does not support 6:6:6 pixel mode.

#### Replacing the ATT20C491 with the IMS G174

The ATT20C491 is an 8-bit DAC device that supports 24-bit true color, 5:6:5 high color mode and 5:5:5 high color mode. The high color and true color modes can be gamma corrected. Overlays are supported in VGA systems.

The IMS G174 can be used as a replacement part for the ATT20C491 if gamma correction is not required. Again the user should be made aware of the differences of programing the Pixel Command register on the IMS G174 and the ATT20C491 as shown in Table 1.2.

#### Replacing the Bt481 with the IMS G174

The Bt481 is an 8-bit DAC device that supports 5:6:5 XGA, 5:5:5 high color modes and 8:8:8:8 true color with overlay. It also incorporates a power down mode.

The Bt481 does not provide multiple mask magic access to program internal registers.

The Bt481 does provide cursor support, through the overlay input pins OL3 and OL2. All cursor registers, apart from cursor colors are no longer valid. The Bt481 can be instructed to be put into XGA cursor compatible mode.

The IMS G174 can be used as a replacement for the Bt481 for high color modes. The true color/8-bit overlay mode cannot be implemented on the IMS G174 as dictated by the Bt481. Use of this true color mode with VGA overlay pixel is limited and has a data throughput drawback (one displayable pixel is latched for four clock edges).

Values for the Pixel Command register which set the Bt481 and IMS G174 into high color modes are very similar, with the exception of true color modes which are incompatible between the two devices.

#### Replacing the Bt482 with the IMS G174

The Bt482 is similar to the Bt481 with the addition of a 32×32×2 onboard cursor which, because of its size, is not XGA compatible.

Most of the implications for using a replacement IMS G174 applying to the Bt481 also apply to the Bt482.

#### 1.2.3 PIXEL MODES

**Definition:** High Color Mode 1

High Color Mode 1 is defined as pixel sampling of LSB of pixel data on rising edge and MSB of pixel data on falling edge of latching pixel data clock.

**Definition:** High Color Mode 2

High Color Mode 2 is defined as pixel sampling of LSB and MSB of pixel data on the rising edge of the latching pixel data clock.

Table 1.2. Comparison of pixel modes on IMS G174, Sierra SC 1148X and AT&T 20C491/2

| Pixel mode                                                            | SGS-THOMSON IMS G174         | Sierra SC 1148X        | AT&T 20C491/2          |

|-----------------------------------------------------------------------|------------------------------|------------------------|------------------------|

| 8bpp pseudo color                                                     | Pixel Command Register = 00h | Command Register = 00h | Control Register = 00h |

| 15bpp high color mode 1                                               | Pixel Command Register = 80h | Command Register = 80h | Control Register = 80h |

| 15bpp high color mode 2                                               | Pixel Command Register = A0h | Command Register = A0h | Control Register = A0h |

| 16bpp high color mode 1                                               | Pixel Command Register = C0h | Command Register = C0h | Not available          |

| 16bpp high color mode 2                                               | Pixel Command Register = E0h | Command Register = E0h | Control Register = C0h |

| 6:6:4 mode high color<br>mode 1                                       | Pixel Command Register = D0h | Not available          | Not available          |

| 6:6:4 mode high color<br>mode 2                                       | Pixel Command Register = F0h | Not available          | Not available          |

| 15-bit pixel with soft-<br>ware PixMix high color<br>mode 1 operation | Pixel Command Register = 88h | Not available          | Not available          |

| 15-bit pixel with soft-<br>ware PixMix high color<br>mode 2 operation | Pixel Command Register = A8h | Not available          | Not available          |

| 24bpp                                                                 | Pixel Command register = B0h | Not available          | Control Register = E0h |

NOTE: To include hardware PixMix function with above pixel modes (except 8bpp) just subtract 80h from values stated above for Pixel Command register

## 1.2.4 PINOUT DIFFERENCES, MEANINGS AND EXTRA PINS

## Differences between Sierra 16-bit Palette-DACs and IMS G174

Setup: Pin 23

This pin tells the device whether to have a 7.5 IRE or 0 IRE blanking pedestal. Equivalent on G174 is **NC**.

OL0-OL3: Pins 41-44

Overlay pins, a fifteen color overlay input which, when a non-zero value has been latched in, will display an overlay color. These functions are disabled on power up. The pins 42, 41 on the G174 (**CD0-1**)

are also ignored on power up and provide cursor plane operation very similar to overlay plane operation.

N/C: Pin 30 (OPA on IMS G174)

For Vref usage this is connected to **Comp**, for Iref usage it is unconnected. See Section 1.4.

Vref: Pin 31 For Vref usage

Same as on G174 Vref version, ignored on Iref ver-

sion

HICOL: Pin 20

Equivalent on G174 is **notPixMix**. **notPixMix** is a superset of the HICOL operation in that it can be enabled during active video operation.

#### Differences between AT&T and IMS G174

OL[3:0] : Pins 41–44, for overlay similar to Sierra operation

TRCTL: Pin 20

Instructs part to select color mode using overlay inputs or control register. Equivalent on IMS G174 is **notPixMix**.

VREF: Pin 31

**Vref** can be connected by a  $0.1\mu F$  capacitor to GND, as proposed by AT&T. However **OPA** must be connected to **Comp** as shown in Section 1.4.

#### 1.2.5 PixMix™

#### What is PixMix?

The IMS G173 and IMS G174 support a facility called PixMix, which allows intermixing of high color and pseudo color on a pixel by pixel basis. This switching can be controlled externally by asserting the **notPixMix** pin on 44 pin PLCC versions of G173 and G174 or through software, by logical detection of bit 15 of a 16-bit high color pixel.

Other similar devices do not provide a PixMix function; many have a pin called HICOL or TRCTL which, when taken active low, place the part in a high color mode, although these devices cannot perform this function on a pixel by pixel basis.

#### Why should you use PixMix?

In a windowing environment it could be a requirement to have windows which have varying pixel format such as a live video insert that uses 24-bit true color or a 15bpp format as opposed to the current 8 bits per pixel. Using the PixMix functions allows this high color insert to appear on a pixel resolution.

For example hardware PixMix could be controlled with the ET4000/W32 BDE pin number 81 by connecting this pin to the **notPixMix** pin of the G174.

If a hardware PixMix function and a 1 bit wide datastore is used as the PixMix source, then arbitrary shapes could be used to describe a high or true color image. Note, that due to the restriction of pins, the hardware PixMix is not available on the G173 28 pin PDIP.

#### 1.2.6 DAC GAIN AND DAC FADE

When using high color (15/16-bit) or true color (24-bit), pixel information is fed directly to the DACs. Because there is no level of indirection through the palette, fading in or out of the display is not possible by programming the palette. However the IMS G174 and IMS G173 have a facility that

allows the user to fade the display in or out. This can be done manually in steps of 1/15th perceived intensity.

Alternatively an automatic fading or gain mechanism can be programmed on the IMS G174 which can be set to operate every two or four or six..... or thirty frames. This automatic fading requires the **notVSync** pin to be connected to the relevant signal. Fading in or out of the DACs will stop either when the DACs are fully blanked, normal intensity is reached or the user aborts the cycle by programming the DAC Fade Register (0Ch).

This facility can be useful in slide presentation application programs requiring a subtle fade in and fade out.

#### 1.2.7 XGA REGISTERS

The IMS G174 contains an XGA compatible cursor palette as described in Section 1.2.8. The IMS G174 provides a means of accessing these registers and others through the XGA style of register access (index and data register are provided). Besides the XGA color cursor registers, the IMS G174 also provides the facility for software written for a multi-tasking environment. A means of reading and setting the state of the microport is provided which can be especially useful when software has been interrupted while trying to read or write values to the palette before completing its access.

The XGA index and data registers can either be accessed directly using extra RS lines, if provided by the controller, or through an extended magic access of the Mask Register. If the Mask Register is read eight times after an initialization phase of the microport and the value 04h is written into the Mask register, then the IMS G174 will be put into XGA mode. The Pixel Mask register now becomes the XGA Index register and the Address (read mode) register becomes the XGA Data register. Details of XGA register index addresses are given in the IMS G174 Datasheet.

#### 1.2.8 XGA CURSOR

The cursor facility is only available on the 44 pin PLCC IMS G174. The cursor data inputs **CD0-1** are latched by PClk in the same way as the rest of the Pixel Interface. Some controllers do provide compatible outputs for usage of an XGA compatible cursor e.g. ET4000/W32 provides two pins SP(0:1) which can be directly connected to the IMS G174 **CD0-1**. Three colors are available to display the cursor. Two are defined as registers on the IMS G174 and the third is the complement of the palette or true color.

## 1.3 USING THE ON-CHIP SELF TEST FACILITIES OF THE IMS G173/4

## 1.3.1 BENEFITS TO THE MANUFACTURER AND END USER

One of the areas of most concern in the computer industry is the area of testability. The ability to accurately test machines accrues benefits to both the manufacturer and end user.

From the manufacturer's point of view, systems having features embodied within them to facilitate testing, can usually be tested quicker than those which do not. This reduces the manufacturing time with a resultant reduction in build cost and increase in manufacturing throughput.

Systems featuring built in self test features which are accessible by the system operating software, BIOS or device driver can incorporate more thorough system diagnostics and power on self test procedures than would otherwise be the case. The ability to perform such diagnostic procedures increases customer perception about the overall machine quality. It is usually impractical however to incorporate additional logic components on the printed circuit board specifically for test purposes, either because of real estate limitations, cost or the unavailability of test access points (if the required data path is not brought out from a device).

The video subsystem by virtue of its shear complexity and data rate imposes an enormous processing requirement upon the system test function. For graphics systems, the integrity of both the host CPU data path and the pixel port data path must be verified.

#### 1.3.2 IMS G173/4 CHECKSUM REGISTERS

The checksum facility provides a mechanism to validate the data being transferred from the controller to the DACs via the pixel port of the G173/4. This validation is performed at real time pixel data rates.

Three 24-bit checksum registers are provided (one for each color channel) and are located in the XGA register space. They are accessed as described in

Section 1.3.4 using the index values shown below in Table 1.3.

Table 1.3. Checksum Registers

| Index Value | Bit | R/W | Function      |

|-------------|-----|-----|---------------|

| Xi86        | 7:0 | R   | RED Byte[0]   |

| Xi87        | 7:0 | R   | RED Byte[1]   |

| Xi88        | 7:0 | R   | RED Byte[2]   |

| Xi89        | 7:0 | R   | GREEN Byte[0] |

| Xi8A        | 7:0 | R   | GREEN Byte[1] |

| Xi8B        | 7:0 | R   | GREEN Byte[2] |

| Xi8C        | 7:0 | R   | BLUE Byte[0]  |

| Xi8D        | 7:0 | R   | BLUE Byte[1]  |

| Xi8E        | 7:0 | R   | BLUE Byte[2]  |

The checksum value is dependent upon:

- Usage of hardware and software PixMix

- Cursor position (if used)

- Interlacing (if used)

It is however independent of sync modes and fly-back patterns.

The registers should be read during frame flyback as described in Section 1.3.4. At other times the checksum registers are accumulating and therefore invalid.

#### Checksum generation

The checksum is generated through a shift register that uses feedback to create a pseudo-random sequence. As each pixel arrives, its 8-bit value is XOR-ed with the lowest 8 bits of the register, and the rest of the register is shifted. The use of feedback minimizes the risk of two errors in the pixel stream cancelling to give a correct checksum value.

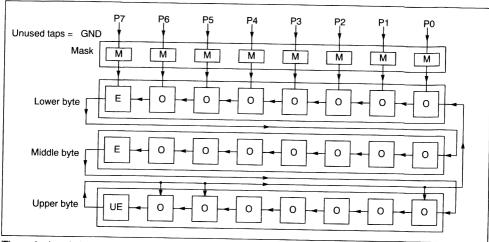

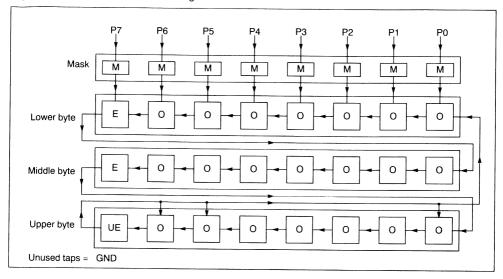

The checksum registers are implemented as Linear Feedback Shift Registers (LFSRs) using the Type II design which use internal Exclusive OR feedback taps as shown in Figure 1.2.

Figure 1.2. Implementation of checksum registers

The calculated checksums for each color channel should equal the contents of the appropriate checksum registers in the device. Clearly if PixMix and/or the cursor channel are used then the algorithm used to calculate the expected checksum values will need to be modified accordingly.

Reading and calculating the contents of the three checksum registers is straightforward. Example C/assembler routines are given in Appendix A.3 to explain how certain required tasks are achieved. These routines have deliberately not been optimized, in order to make their function obvious. Note that for simplicity the checksums have all been read and calculated using a blank screen and border, with (0, 0, 0) in palette location 0, and with no cursor or overlays. Clearly checksums can be generated for any image or display, and this would typically yield different values for each of the three colors.

#### 1.3.3 CALCULATING THEORETICAL CHECK-SUM VALUES

The theoretical checksums can be calculated for a given screen size as shown in Appendix A.3.4. Note that with (S)VGA systems, the border (usually black) is passed through the Palette-DAC as normal pixels. Border pixels are consequently used in the hardware checksum calculations, and therefore must be included when calculating the theoretical value. Note also that if the display is interlaced, then the hardware checksum must be accumulated over two frames (fields in this case), as only the odd (or even) lines will have been included during one frame.

The steps that should be followed are:

- 1 Determine if border present, if so, determine size (left, right, top, bottom).

- 2 Calculate theoretical checksum values (using border, screen and palette).

#### **Border calculation**

The left and right borders (in pixels), and top and bottom borders (in lines) are readily calculated by reading the relevant timing registers in the (S)VGA CRT controller.

These registers are described in the standard VGA specification, consequently these calculations should be portable across different VGA controllers.

To access these CRT indexed registers, the index must be output to address 3D4h, then the register is accessed at address 3D5h.

hbe = horizontal blank end (CRT index 03h)

hbs = horizontal blank start (CRT index 02h)

hde = horizontal display end (CRT index 01h)

The horizontal registers are in units of 8 pixels. The htot register is 5 less then the real horizontal total

(for VGA). Note that the horizontal blank end register is only the lower 5 bits of the register (upper bits are elsewhere) – for convenience only these bits have been considered here, although strictly speaking the upper bits should have been included.

Where: vtot = vertical total (CRT index 06h)

vbe = vertical blank end (CRT index 16h)

vbs = vertical blank start (CRT index 15h)

vde = vertical display end (CRT index 12h)

Note that the vtot register is 2 less than the actual vertical total number of lines (for VGA).

#### Calculated checksum examples

For convenience, the following checksum examples have been calculated using a black and then a white screen, and with the border color set to black. This means that the checksums for all three colors are the same

#### 640×480, 8bpp

left border = 8 pixels, right border = 8 pixels top border = 8 lines, bottom border = 8 lines

So the theoretically calculated checksum must be calculated for a screen size of 656 by 496.

Checksum = 2CC153h (black, RGB) Checksum = 84E438h (white, RGB).

#### 800×600, 8bpp

left border = 8 pixels, right border = 8 pixels top border = 4 lines, bottom border = 4 lines

So the theoretically calculated checksum must be calculated for a screen size of 816 by 608.

Checksum = 338ED5h (black, RGB) Checksum = 3A90B8h (white, RGB).

#### 1024×768, 8bpp

(Note this may be interlaced on some graphics cards)

left border = 0 pixels, right border = 0 pixels top border = 0 lines, bottom border = 0 lines

So the theoretically calculated checksum must be calculated for a screen size of 1024 by 768.

Checksum = 442B24h (black, RGB) Checksum = 0CDBC1h (white, RGB).

#### 1.3.4 READING THE HARDWARE CHECK-SUMS FROM THE IMS G174

The steps for this are:

- 1 Wait for frame flyback

- 2 Reset the checksum registers (in XGA mode)

- 3 Wait for frame flyback

- 4 Read the checksums (in XGA mode)

#### XGA mode

In order to access the checksum registers in the IMS G174, the device must be put into XGA mode. This is easily achieved, and is demonstrated in Appendix A.3.1:

The steps to put the IMS G174 into XGA mode are:

- 1 Access the XGA enable register by reading the Pixel Mask Register eight times.

- 2 Put the device into XGA mode by setting the XGA enable bit (bit 2, i.e. write 04h into the XGA enable register).

- 3 Set bit 7 in the Test Control Register (write 80h into XGA indexed register 80h).

Note step 3 must be done where the VGA controller does not allow read access to 3C7h. This puts the device into a special mode where read/write accesses to 3C8h and 3C9h actually access the registers normally appearing at 3C6h and 3C7h.

After step 3 the XGA index is accessed at address 3C8h, and the XGA data is accessed at address 3C9h.

#### Resetting the checksum registers

Before the checksums can be read, they must be reset (to FFFFFh), then allowed to accumulate over a frame.

To reset the checksums to FFFFFFh, as they are read only, a special bit exists (bit 5, XGA index 80h). The procedure is demonstrated in Appendix A.3.6. The checksums must be reset on entering frame flyback, as otherwise they will start accumulating their values. Note that bit 5 is set high, then set low, without altering the state of the register (which will either be 00h or 80h, as mentioned above).

#### 1.3.5 READING THE CHECKSUM REGISTERS

Reading the checksum registers is straightforward, bearing in mind that all accesses must be XGA indexed, and that they should only be read during frame flyback. The procedure is demonstrated in Appendix A.3.7. First the XGA index must be output to the (new) XGA index register, then the appropriate byte can be read back.

Note that this must all be accomplished within frame flyback, as otherwise invalid data will be read, due to the checksum mechanism accumulating during active display.

If due to processor speed and system considerations, it is not possible to read all three checksums during a single frame flyback, then the example code could be divided to reset the checksums, then read a single color per frame flyback. Clearly the screen and palette, cursor etc. must be held constant during this time.

#### Checksums with interlaced displays

When the display is interlaced, the checksum registers must be allowed to accumulate over two frames (fields).

Also because it may not be possible to determine the field order presented to the Palette-DAC, the checksum mechanism may accumulate the checksum value in a different field order from that used in the theoretical calculation. Clearly the field order will be correct for half the time. The example program shown in Appendix A.3.4 for simplicity does not cater for interlaced displays. Obviously where the fields are identical (such as on an all black or all white screen) then the field order is irrelevent. Two theoretical checksums could be calculated, one for each of the field orders.

#### 6-bit palette operation

Note that in 6-bit palette operation mode the color field written to the palette (6 bits right justified in an 8-bit field) will be presented to the checksum mechanism left justified in an 8-bit field.

#### 1.3.6 VGA MODE

In order to return the device into VGA mode, the XGA enable bit in the XGA enable register must be set low, i.e. 00h must be written into the XGA enable register. This is actually achieved in a similar way to putting the device into XGA mode, except that the mask register must be accessed as an XGA indexed register, and cannot be accessed at address 3C6h as would normally be performed if the part was in VGA mode. 3C6h is of course the original XGA index port in XGA mode. This procedure is demonstrated in Appendix A.3.2.

#### Wait for frame flyback

It is important that the checksum registers are only reset and read during frame flyback. For convenience, a method for synchronizing to frame flyback is shown in Appendix A.3.3. To avoid the possibility of synchronizing to an indeterminate position during frame flyback, it is necessary to first wait for active display, followed by frame flyback. At this point frame flyback will always have just started.

#### 1.4 ANALOG CONSIDERATIONS

#### 1.4.1 SUMMARY

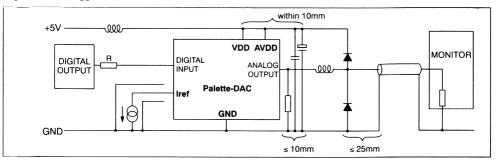

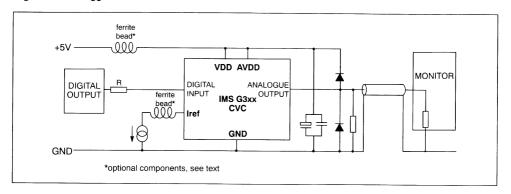

Figure 1.3. Suggested circuit

#### 1.4.2 COMPONENT PLACEMENT

Do keep all Palette-DAC circuitry as close as possible to the output connector to reduce noise pickup and reflections incurred by impedance mismatches. This will also reduce the risk of RFI problems. Keep the DAC termination resistors within 10mm of the DAC outputs to optimize the edge rate performance.

Do keep the current or voltage reference circuitry as close as possible to the Palette-DAC to reduce pickup (within 10mm maximum). For the same reason the Iref or Vref track should not be near any pixel rate signals but should be shielded by GND running either side of it.

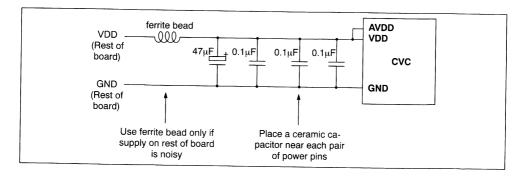

#### 1.4.3 POWER SUPPLY REQUIREMENTS

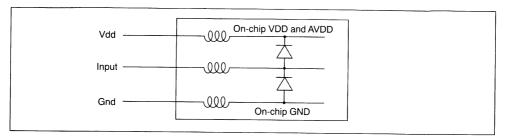

Use VDD and GND power planes to ensure a low inductance supply and reduce RFI emissions.

Use a separated analog VDD plane for the Palette-DAC, connected to the main VDD plane by a ferrite bead (value 0.35 $\mu$ H, impedance about 100 $\Omega$  at 100MHz). The **VDD** and **AVDD** pins of the Palette-DAC should be connected to this plane. Digital signals should not overlay the analog power plane any more than necessary. To ensure minimum pickup from digital signals, this analog plane can be just under the analog pins of the Palette-DAC and all **VDD** pins.

Use a single  $47\mu\text{F}$  tantalum near to the Palette-DAC for general power plane decoupling, and  $0.1\mu\text{F}$  ceramic chip capacitors immediately adjacent to every pair of **VDD** and **GND** pins.

Do solder the device directly into the PCB to reduce power supply inductance and maximize the effect of the power supply decoupling.

#### 1.4.4 DAC OUTPUTS

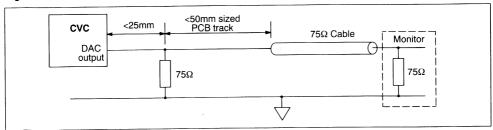

DAC termination resistors should be high-accuracy specification and placed within 10mm of the DAC outputs.

Do use double termination as this optimizes the DAC edge rates due to the lower RC time constant and is also more tolerant of impedance mismatches.

The PCB tracks from the termination resistors to the video connector should be sized to form a transmission line of the required impedance. Even so, these traces should still be less than 25mm long to reduce the effect of mismatches and reflections.

Protection diodes to the power rails are recommended at the analog outputs.

#### 1.4.5 DIGITAL INPUTS

Do keep fast digital signals away from sensitive analog circuitry.

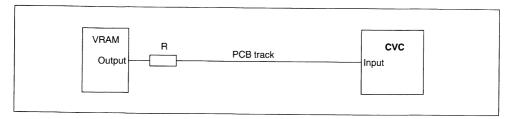

The signals most likely to cause problems are the pixel inputs. Do keep the pixel input buffers close to the Palette-DAC to minimize ringing and therefore undershoot and overshoot. If fast drivers are required to achieve timing requirements, a series termination resistor (normally  $10-100\Omega$ ) helps.

Use the slowest edge rates of signals possible to meet the product datasheet timings. This will cause less RFI and less disturbance of the power supply. Slower speed logic families may often improve overall display quality.

#### 1.4.6 RFI

Keep tracks leading to and from the Palette-DAC short, particularly the pixel address, pixel clock and DAC outputs.

Always use at least a four-layer board with VDD and GND planes. Ensure good VDD and GND decoupling.

Avoid flying leads carrying high frequency signals which are not screened.

Place load resistors as close as possible to the analog outputs.

Use slower speed logic families wherever possible.

#### 1.4.7 REFERENCE CIRCUITRY

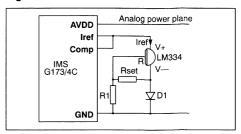

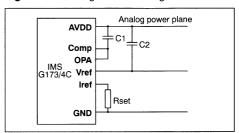

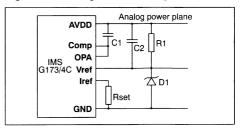

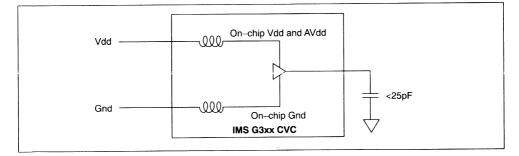

Most SGS-THOMSON Palette-DACs can only use Iref reference circuitry. The G173/4C can use internal or external Vref circuitry. For Vref systems an external Vref circuit is recommended for optimum DAC performance.

External reference circuitry must be placed within 10mm of the Palette-DAC. Reference signals must be shielded and not be near digital signals.

The following values apply to Iref and Vref circuits:

**Vpeakwhite** Vpeakwhite is the peak analog DAC output voltage, including any sync pedestal voltages. On the SGS-THOMSON IMS G17x series of Palette-DACs, sync pedestals are not available and Vpeakwhite will typically be 0.7V.

**Rload** Rload is the effective load resistance on the analog outputs. If using a doubly terminated 75 $\Omega$  load, Reffective is 37.5 $\Omega$ .

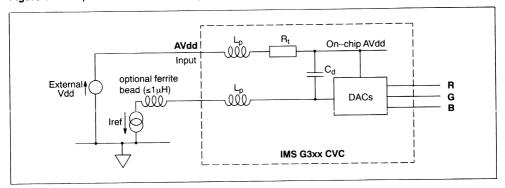

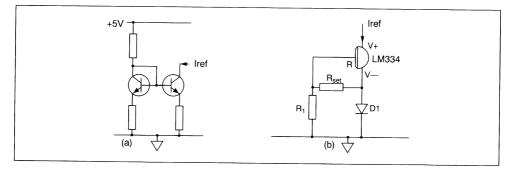

#### Current reference circuit (Figure 1.4)

Iref = Vpeakwhite/2.1 × Rload

For Iref systems pin 28 must be connected to 29. An LM334 circuit is recommended (see Fig 1.4) with no decoupling capacitors at all connected to the **Iref** input. If there is excessive noise on the Iref input it is possible to connect a  $0.1\mu F$  chip capacitor in parallel with a  $47\mu F$  tantalum capacitor between **Iref** and **AVDD**. High frequency noise in the current reference may be further removed by using a ferrite bead (less than  $1\mu H$ ) in series in the Iref line.

Diode D1 provides temperature compensation - a 1N4148 or equivalent should be used. The ratio of R1 to Rset determines the amount of temperature compensation - typically R1 should be 10Rset, but the optimum ratio should be found by experiment. See the LM334 datasheet for further details.

#### Voltage reference circuits (Figures 1.5, 1.6)

Rset =  $1.235 \times 2.1 \times \text{Rload} / \text{Vpeakwhite}$

Figure 1.4. Current reference circuit

Table 1.4. External Iref components

| Component | Value                | Description |

|-----------|----------------------|-------------|

| R1        | 150Ω                 | 1% resistor |

| Rset      | 15Ω                  | 1% resistor |

| D1        | 1N4148 or equivalent | diode       |

Figure 1.5. Using Internal Voltage reference

Table 1.5. Internal Vref components

| Component | Value               | Description       |

|-----------|---------------------|-------------------|

| C1-C2     | 0.1μF               | ceramic capacitor |

| Rset      | 140Ω (see equation) | 1% resistor       |

Figure 1.6. Using External Voltage reference

Table 1.6. External Vref components

| Component | Value               | Description       |

|-----------|---------------------|-------------------|

| C1-C2     | 0.1μF               | ceramic capacitor |

| R1        | 1ΚΩ                 | 1% resistor       |

| Rset      | 140Ω (see equation) | 1% resistor       |

| D1        | 1.2V                | voltage reference |

#### A APPENDIX

### A.1 EXAMPLE ROUTINE TO SET PIXEL COMMAND AND MASK REGISTERS TO POWER-UP VALUES

Normally after power-up the Pixel Command Register and Mask Register will be 0h and 0FFh respectively. If the contents of these registers is in doubt for any reason then the following routine will ensure that they are both set to their power-up values.

```

; clean start, mask := ff, cmd reg := 0

mov dx, 03c9h

in al, dx

; reset seq

mov dx, 03c6h

in al, dx

in al, dx

in al, dx

in al, dx

mov al, 0

out dx, al

; cmd reg := 0

mov dx, 03c9h

in al, dx

; reset seq

mov dx, 03c6h

mov al, Offh

out dx, al

; mask := ff

```

#### A.2 EXAMPLE ROUTINE TO IDENTIFY THE PALETTE-DAC

Shown below is an example routine to identify the Palette-DAC, as discussed in Section 1.2.1.

```

; start of dac id example routine

; read cmd reg twice

mov dx, 03c6h

in al, dx

in al, dx

in al, dx

in al, dx

; music gives id here, #88 / #89

mov bl, al

in al, dx

; 1st cmd reg read

mov bh, al

in al, dx

; 2nd cmd reg read

mov cl, al

in al, dx

; 3rd cmd reg read

in al, dx

; 4th cmd reg read

; 5th cmd reg read

in al, dx

in al, dx

; 6th cmd reg read

mov ch, al

; is it a hi color DAC ?

cmp bh, Offh

jnz iddac_hi_color

mov al, not_hi_color_DAC

imp iddac exit

iddac hi color:

cmp bl, Offh

; music ?

jz iddac not music

mov al, music hi color DAC

jmp iddac exit

```

iddac not music:

```

cmp bh, cl

; sierra ?

jnz iddac not sierra

cmp bh, ch

jnz iddac_not_sierra

mov al, sierra hi color DAC

jmp iddac_exit

iddac not sierra:

; save palette [1]

mov dx, 03c7h

; read index

; set location index

mov al, 1

out dx, al

mov dx, 03c9h

; data

in al, dx

mov bl, al

; save r

in al, dx

mov bh, al

; save g

in al, dx

mov cl, al

; save b

; palette [1] := ff

mov dx, 03c8h

; write index

; set location index

mov al, 1

out dx, al

mov dx, 03c9h

; data

mov al, Offh

; set to ff, ff, ff

out dx, al

out dx, al

out dx, al

; read palette [1]

mov dx, 03c7h

; read index

mov al, 1

out dx, al

mov dx, 03c9h

; data

in al, dx

mov ch, al

; put back contents of palette [1]

mov dx, 03c8h

; write index

mov al, 1

; set location index

out dx, al

mov dx, 03c9h

; data

mov al, bl

; r

out dx, al

mov al, bh

; g

out dx, al

mov al, cl

; b

out dx, al

; hardwired 8not6 pin ?

cmp ch, 03fh

jz iddac_not_hard_wired

mov al, unidentified DAC

; 8not6 pin is hardwired to vcc

jmp iddac exit

iddac_not_hard_wired:

; cmd reg := 2

mov dx, 03c6h

```

```

in al, dx

in al, dx

in al, dx

in al, dx

mov al, 02h

; set soft 8 bit palette att

out dx, al

; save palette [1]

mov dx, 03c7h

; read index

mov al, 1

; set location index

out dx, al

mov dx, 03c9h

; data

in al, dx

mov bl, al

; save r

in al, dx

mov bh, al

; save q

in al, dx

mov cl, al

; save b

; palette [1] := ff

mov dx, 03c8h

; write index

mov al, 1

; set location index

out dx, al

mov dx, 03c9h

; data

mov al, Offh

; set to ff, ff, ff

out dx, al

out dx, al

out dx, al

; read palette [1]

mov dx, 03c7h

; read index

mov al, 1

out dx, al

mov dx, 03c9h

; data

in al, dx

mov ch, al

; put back contents of palette [1]

mov dx, 03c8h

; write index

mov al, 1

; set location index

out dx, al

mov dx, 03c9h

; data

mov al, bl

; r

out dx, al

mov al, bh

; g

out dx, al

mov al, cl

; b

out dx, al

and ch, Ofch

; att ?

cmp ch, Ofch

jnz iddac_not_att

mov al, att_hi_color_DAC

jmp iddac exit

iddac_not_att:

; cmd reg := ff

mov dx, 03c6h

```

```

n al, dx

in al, dx

in al, dx

in al, dx

mov al, Offh

out dx, al

; read cmd reg

mov dx, 03c6h

in al, dx

mov ch, al

cmp ch, 0bh

; acumos ?

jnz iddac not acumos

mov al, acumos_hi_color_DAC

jmp iddac_exit

iddac_not_acumos:

cmp ch, Offh

jnz iddac_not_inmos

mov al, inmos hi color DAC

jmp iddac exit

iddac_not_inmos:

mov al, unidentified DAC

iddac exit:

End of example routine.

A.3 EXAMPLE PROGRAMS FOR READING AND CALCULATING CHECKSUMS

A.3.1 SETTING THE G174 INTO XGA MODE

void put g174 into xga mode ()

/* assume we are in vga mode */

asm mov dx, 0x03c7 /* reset seq */

asm in al, dx

asm mov dx, 0x03c6

/* 4 reads of mask reg -> pix cmd reg */

asm in al, dx

/* 4 reads of pix cmd reg -> xga enable reg */

asm in al, dx

asm in al, dx

asm in al, dx

asm mov al, 4

/* set bit 2 hi for xga mode */

asm out dx, al

asm mov al, 0x080

asm out dx, al

asm mov dx, 0x03c9

asm out dx, al

}

```

```

A.3.2 SETTING THE G174 INTO VGA MODE

void put_g174 into_vga_mode ()

{

/* assume we are in xga mode */

asm mov dx, 0x03c8 /* xga index reg */

/* mask index */

asm mov al, 0x064

asm out dx, al

asm mov dx, 0x03c9 /* xga data reg */

/* 4 reads of mask reg -> pix cmd reg */

asm in al, dx

asm in al, dx

asm in al, dx

asm in al, dx

/* 4 reads of pix cmd reg -> xga enable reg */

asm in al, dx

asm in al, dx

asm in al, dx

asm in al, dx

asm mov al, 0

/* set bit 2 lo for vga mode */

asm out dx, al

}

A.3.3 WAITING FOR FRAME FLYBACK

void wait for frame flyback ()

/* use the vertical retrace when bit vr == 1

* wait for 0 (video data), then wait for 1 (blanking),

char bit vr;

volatile char byte;

asm mov dx, 0x03da

asm in al, dx

asm mov byte, al

bit vr = (byte >> 3) & 1;

while (bit_vr == 1) /* wait for active display */

asm mov dx, 0x03da

asm in al, dx

asm mov byte, al

bit vr = (byte >> 3) & 1;

asm mov dx, 0x03da

asm in al, dx

asm mov byte, al

bit vr = (byte >> 3) & 1;

while (bit_vr == 0) /* wait for frame flyback */

asm mov dx, 0x03da

asm in al, dx

asm mov byte, al

bit vr = (byte >> 3) & 1;

}

}

```

```

A.3.4 CHECKSUM CALCULATION

void calculate_chksums (long int results [3],

int screen_width, int screen height,

char palette [256][3])

{

/* here screen_width and screen_height must include the borders */

int color, x, y;

for (color = 0; color < 3; color++) /* reset checksums */

results [color] = 0x0FFFFFFL;

for (y = 0; y < screen height; y++)

for (x = 0; x < screen width; x++)

{

char pixel;

if (on_screen)

/* valid pixel */

pixel = read_pixel (x, y);

else

/* else border pixel */

pixel = 0;

for (color = 0; color < 3; color++)

results [color] ^= (long) (palette [(int) pixel] [color] << 2);

results [color] <<= 1;

if ((results [color] & 0x01000000L) == 0)

results [color] |= 1;

results [color] ^= (long) 0x0c20000L;

results [color] &= (long) 0x0FFFFFFL;

plot_pixel (0, y, 255); /* progress indicator, plot on line done */

}

A.3.5 BORDER CALCULATION

/* calculate right hand border */

char hde, hbs;

asm mov dx, 0x03d4

asm mov al, 0x02

/* hor blnk start index */

asm out dx, al

asm mov dx, 0x03d5

asm in al, dx

asm mov hbs, al

asm mov dx, 0x03d4

asm mov al, 0x01

/* hor disp end index */

asm out dx, al

asm mov dx, 0x03d5

asm in al, dx

asm mov hde, al

border_right = (hbs - hde) * 8; /* 8 pixels per char */

}

```

```

/* calculate left hand border */

char hbe, htot;

asm mov dx, 0x03d4

asm mov al, 0x03

/* hor blnk end index */

asm out dx, al

asm mov dx, 0x03d5

asm in al, dx

asm mov hbe, al

asm mov dx, 0x03d4

asm mov al, 0x00

/* hor tot index */

asm out dx, al

asm mov dx, 0x03d5

asm in al, dx

asm mov htot, al

border_left = (((htot + 5 - 1) & 0x01f) - (hbe & 0x01f)) * 8;

}

/* calculate bottom border */

char vde, vbs;

asm mov dx, 0x03d4

asm mov al, 0x15

/* vert blnk start index */

asm out dx, al

asm mov dx, 0x03d5

asm in al, dx

asm mov vbs, al

asm mov dx, 0x03d4

asm mov al, 0x12

/* vert disp end index */

asm out dx, al

asm mov dx, 0x03d5

asm in al, dx

asm mov vde, al

border bot = vbs - vde;

/* calculate top border */

char vbe, vtot;

asm mov dx, 0x03d4

/* vert blnk end index */

asm mov al, 0x16

asm out dx, al

asm mov dx, 0x03d5

asm in al, dx

asm mov vbe, al

asm mov dx, 0x03d4

/* vert total index */

asm mov al, 0x06

asm out dx, al

asm mov dx, 0x03d5

asm in al, dx

asm mov vtot, al

border_top = (vtot + 2 - 1) - vbe;

}

```

```

A.3.6 RESETTING CHECKSUMS

void reset_chksums ()

put_g174_into_xga_mode ();

wait for frame_flyback ();

asm mov dx, 0x03c8

asm mov al, 0x080

/* index of test reg */

asm out dx, al

asm mov dx, 0x03c9

/* read previous value */

asm in al, dx

/* set bit */

asm or al, 0x020

asm out dx, al

asm and al, 0x0df /* reset bit */

asm out dx, al

put g174 into_vga mode ();

}

A.3.7 READING CHECKSUMS

void read_the_chksums (long int chksums [3])

char red byte 0,

red_byte 1,

red byte 2;

char green_byte_0, green_byte_1, green_byte_2;

char blue_byte_0, blue_byte_1, blue byte 2;

put_g174_into_xga_mode ();

wait for frame flyback ();

/*wait_for_frame_flyback ();*/ /* interlaced mode only */

asm mov dx, 0x03c8

asm mov al, 0x086

/* red byte 0 */

asm out dx, al

asm mov dx, 0x03c9

asm in al, dx

asm mov red_byte 0, al

asm mov dx, 0x03c8

asm mov al, 0x087

/* red byte 1 */

asm out dx, al

asm mov dx, 0x03c9

asm in al, dx

asm mov red byte 1, al

asm mov dx, 0x03c8

asm mov al, 0x088

/* red bvte 2 */

asm out dx, al

asm mov dx, 0x03c9

asm in al, dx

asm mov red byte 2, al

asm mov dx, 0x03c8

asm mov al, 0x089

/* green byte 0 */

asm out dx, al

asm mov dx, 0x03c9

asm in al, dx

asm mov green byte 0, al

asm mov dx, 0x03c8

/* green byte 1 */

asm mov al, 0x08a

asm out dx, al

asm mov dx, 0x03c9

```

```

asm in al, dx

asm mov green_byte 1, al

asm mov dx, 0x03c8

/* green byte 2 */

asm mov al, 0x08b

asm out dx, al

asm mov dx, 0x03c9

asm in al, dx

asm mov green_byte_2, al

asm mov dx, 0x03c8

/* blue byte 0 */

asm mov al, 0x08c

asm out dx, al

asm mov dx, 0x03c9

asm in al, dx

asm mov blue_byte 0, al

asm mov dx, 0x03c8

/* blue byte 1 */

asm mov al, 0x08d

asm out dx, al

asm mov dx, 0x03c9

asm in al, dx

asm mov blue_byte_1, al

asm mov dx, 0x03c8

/* blue byte 2 */

asm mov al, 0x08e

asm out dx, al

asm mov dx, 0x03c9

asm in al, dx

asm mov blue byte_2, al

chksums [0] = (long) red_byte_0 | (((long) red_byte_1 | ((long)

red byte 2 << 8)) << 8);

chksums [1] = (long) green_byte_0 | (((long) green_byte_1 | ((long)

green_byte_2 << 8)) << 8);

chksums [2] = (long) blue_byte_0 | (((long) blue_byte_1 | ((long)

blue byte_2 << 8)) << 8);

put_g174_into_vga_mode ();

```

### **APPLICATION NOTE**

### **DESIGNING WITH THE IMS G177**

| 2.1 | INTRO | DUCTION                                                         | 38 |

|-----|-------|-----------------------------------------------------------------|----|

| 2.2 | INTER | FACING TO THE VGA CHIPSET                                       | 38 |

|     | 2.3   | INTERFACING THE IMS G177 TO THE CIRRUS LOGIC 610/620            | 38 |

|     | 2.4   | INTERFACING THE IMS G177 TO THE CHIPS AND TECHNOLOGIES 82C455/6 | 38 |

| 2.5 | REPLA | ACING OTHER PALETTE-DACS                                        | 39 |

|     | 2.6   | REPLACING THE AMD AM81EC176 WITH THE SGS-THOMSON IMS G177       | 39 |

|     | 2.7   | REPLACING THE BROOKTREE BT475 WITH THE SGS-THOMSON IMS G177     | 39 |

|     | 2.8   | REPLACING THE AVASEM AV36L77 WITH THE SGS-THOMSON IMS G177      | 39 |

#### 2.1 INTRODUCTION

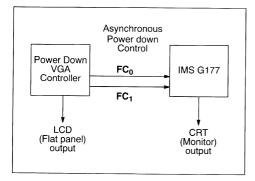

The IMS G177 has been specifically designed for lap top, notebook and all other types of portable PC. The G177 produces a high quality analog output to drive a conventional full color VGA monitor, giving the portable PC a standard and quality of graphics output that is comparable with any highend VGA desk-top PC. The IMS G177 also boasts the world's lowest power consumption and smallest package for a 6-bit Palette-DAC, down to typically  $5\mu$ A.

For ease of design the G177 is completely backwards compatible with the SGS-THOMSON IMS G176, the industry standard Palette-DAC for VGA graphics. The power-down features of the G177 are controlled by two Feature Control pins (FC[0] and FC[1]) which operate asynchronously. The two pins are simply connected directly to the VGA Controller without any extra hardware or software overheads.

Figure 2.1. Ease of interfacing the IMS G177

#### 2.2 INTERFACING TO THE VGA CHIPSET

### 2.3 INTERFACING THE IMS G177 TO THE CIRRUS LOGIC 610/620

The Cirrus Logic VGA chip set has two bits in the Feature Control Register which can be assigned as general purpose outputs. The Cirrus Logic Power Down VGA chip set ('C' revision) has a standard BIOS which defines these pins to be directly compatible with the G177. The two pins on the 'B' revision chip set are programmable and can be initiated to be fully compatible with the G177. In such a configuration, the FC[1:0] outputs on pins 4, 5 of the CL-GD610-C (and pins 20, 21 of the standard CL-GD610) can be connected directly to the FC[1:0] inputs of the IMS G177 (pins 15, 17).

The G177 and CL-610/620-C solution provides a very low power implementation while providing an extremely high quality combination of graphics outputs.

### 2.4 INTERFACING THE IMS G177 TO THE CHIPS AND TECHNOLOGIES 82C455/6

Two pins on the Chips and Technologies chip set (called **ERMEN**/ and **TRAP**/) can be redefined as general purpose outputs. It is suggested by Chips and Technologies that **TRAP**/ be redefined as an **CRT/LCD** information strobe, although the sense would need to be inverted from that normally provided to connect to the **FC[0]** pin of the G177. Therefore to directly connect the 82C455/6 the G177 it is recommended that:

ERMEN/ be redefined as PWRDN[2]

TRAP/ be redefined as LCD/CRT

ERMEN/ = FC[1]

TRAP/ = FC[0]

with re-definitions programmed when the 82C455/6 is initialized.

There are other solutions open to the designer. If the user requires that **ERMEN**/ and **TRAP**/ remain undefined or at their default use, then some of the *inputs* to the 82C455/6 can be used instead. The 82C455/6 enter different power management states according to the state of two input pins (or one pin, depending on the device in question). The interpretation of these pins is not programmable but they can be tapped off as inputs to the IMS G177.

#### 82C456 Two Available States

With direct connections of:

VDD = FC[1] PWRDN[2] = FC[0]

the G177 will enter REVIEW mode when the 82C456 enters Retire (fully off) mode.

#### 82C455 Three Available States

With the addition of an inverter to provide the state of **PWRDN[2]** you can connect:

PWRDN[2] = FC[1] PWRDN[1] = FC[0]

Under these conditions the G177 will correctly interpret the Chips and Technologies NORMAL, RELAX and RETIRE modes as the G177's NORMAL, REVIEW and STANDBY modes respectively.

#### 2.5 REPLACING OTHER PALETTE-DACS

The SGS-THOMSON IMS G177 can replace the Brooktree Bt475, AMD Am81EC176 and other Palette-DACs to provide an elegant, high quality solution with greatly reduced power consumption and other features especially tailored for portable PCs.

#### 2.6 REPLACING THE AMD Am81EC176 WITH THE SGS-THOMSON IMS G177

The G177 is a pin for pin replacement for the AMD Am81EC176 and does not require any redesign effort. However, the G177 consumes significantly less power than the AMD device and also includes integrated comparators for space saving and cost reduction.

The connections made are:

VDD=FC[1] SLEEP=FC[0]

### 2.7 REPLACING THE BROOKTREE Bt475 WITH THE SGS-THOMSON IMS G177

The Brooktree device requires a software overhead to access the control register to control its power management function. This is not a preferred option for the IMS G177 as direct connection to the hardware leads to a simpler interface between the Palette-DAC and the rest of the system hardware and software. Powering down of screens and control of the IMS G177 can be achieved without software action by the use of the asynchronous Feature Control (FC) input pins. The VGA controllers take in and/or provide pins which can be used directly for the G177, giving effortless asynchronous operation for all modes. This is described in more detail in the previous sections.

The IMS G177 consumes significantly less power than the Bt475, does not require additional external circuitry to turn the current reference off during sleep mode and occupies around half the area of the Brooktree package.

#### 2.8 REPLACING THE AVASEM AV36L77 WITH THE SGS-THOMSON IMS G177

The IMS G177 is pin and function compatible with the AV36L77. Using the G177 is therefore simply a matter of substitution, and provides a reduction in power consumption from typically 10mA to  $130\mu$ A or from 1mA to  $5\mu$ A depending on the standby mode used.

# **CVC APPLICATION NOTES**

### **APPLICATION NOTE**

# 32-BIT COLOR VIDEO CONTROLLER UPGRADE COMPATIBILITY: A DESIGN GUIDE

### GRAPHICS APPLICATIONS GROUP, BRISTOL

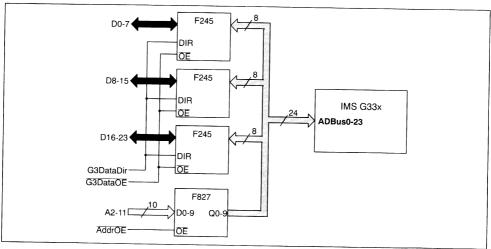

| 3.1         | INTROI | DUCTION                                                     | 44 |

|-------------|--------|-------------------------------------------------------------|----|

|             | FFATU  | RES OF THE COLOR VIDEO CONTROLLER                           | 44 |